引言

针对上述需求,当前的主流技术方案是将回波信号采集装置置于屏蔽室,靠近接收线圈,并通过光纤传输采集后的回波数据.近年来基于Xilinx公司Aurora协议的高速串行通信在磁共振光纤数据传输中有所应用[11⇓-13],但该协议没有差错控制机制,传输的可靠性需要补充判别功能加以保证[14],导致现场可编程门阵列(Field Programmable Gate Array,FPGA)编程复杂.华东师范大学的研究团队提出了一种磁共振多通道数字传输系统及数据传输方法[15,16],实现了回波数据的高速传输,但其方案没有数据错误检测和流控制等链路稳定功能.国外磁共振成像仪器厂商(如GE、西门子等)在他们的新一代系统中应用了光纤数据传输技术,但是相关技术细节没有对外发表.

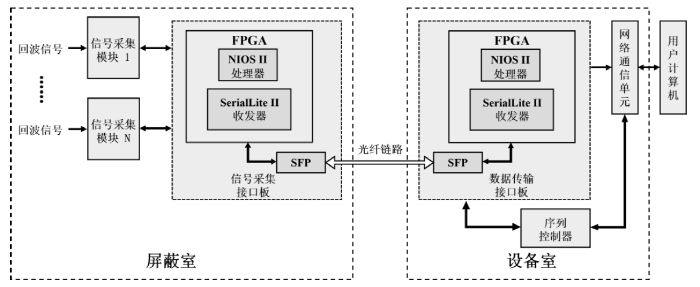

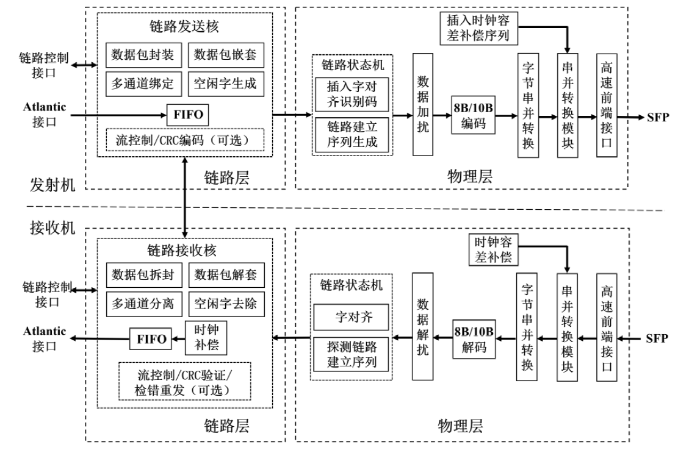

为了实现磁共振成像信号采集过程中高速而可靠的光纤数据传输,本文提出了基于Altera公司(现属于Intel公司)SerialLite II协议[17]的数据传输方案,并开发了数据传输系统.位于屏蔽室的信号采集接口板(与各通道的信号采集模块连接)通过光纤与位于谱仪控制台的数据传输接口板互连,实现配置参数的下传与回波数据的上传,两块接口板均以FPGA器件为核心,运行SerialLite II数据传输协议,该协议具有高速率、低时延等特点,并且具备检错重传和流控制等功能[18].为了方便编程与提高设备紧凑度,在两边的FPGA中均实现了一个软核处理器—NIOS II[19,20],以实现配置参数的发送、接收与设置.该数据传输系统能够可靠地实现参数下传与回波数据上传,数据传输的时间消耗很小.当前,信号采集接口板连接四个信号采集模块(采集低场磁共振信号),未来可以将多个通道的采集集成于一个信号采集模块,同时配备变频电路,这样就能够实现对高场条件下更多通道磁共振信号的采集与传输.

1 数据传输系统的电路设计

1.1 总体结构

基于光纤的磁共振成像数据传输系统的总体结构如图1所示. 数据传输系统由两块接口板组成:一块为信号采集接口板,位于屏蔽室中;一块为数据传输接口板,位于设备室的谱仪控制台之中.成像序列运行之前,由序列控制器将用于信号采集的配置参数写到数据传输接口板的NIOS II处理器中,配置参数主要包括信号放大的增益、数字接收机的参数(包括本振频率与相位、抽取的系数、以及滤波器的系数等),NIOS II处理器将配置参数通过SerialLite II收发器发送到小型可插拔(Small Form Pluggable,SFP)光模块,通过光纤输出.信号采集接口板上的NIOS II处理器接收到配置参数后,开始逐个配置通道1至通道N上的信号采集模块.成像序列运行时,信号采集接口板接收每个通道的I/Q数据,然后将数据打包并经过SerialLite II收发器发送到SFP光模块,通过光纤传送到数据传输接口板,并由网络通信单元发送到用户计算机,由用户计算机进行图像重建.

图1

图1

磁共振成像数据传输系统的总体结构

Fig. 1

The overall structure of magnetic resonance imaging data transmission system

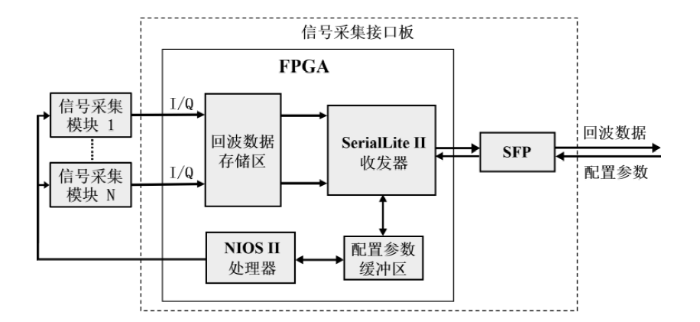

1.2 信号采集接口板

信号采集接口板采用Altera公司的Arria II GX系列的EP2AGX65芯片作为核心,该芯片集成了50 600个逻辑单元,4.56 Mbit内存,内嵌8个IP硬核高速收发口,单口数据传输速率高达3.75 Gbps.光模块采用Avago公司的AFCT-5705LZ,其为单模1310 nm SFP模块,发射口差分输入电压范围为0.5~2.4 V,接收口差分输出电压范围为0.37~1.6 V,收发口电压范围与SerialLite II协议下FPGA高速收发器的1.4 V伪电流模式逻辑(Pseudo Current Mode Logic,PCML)电平匹配.在FPGA中构建NIOS II软核处理器,这是一个具有哈佛结构、32位指令集的处理器.根据信号采集模块的配置需要,除了核心处理器外,还添加了指令随机存取存储器(Random Access Memory,RAM)、可编程的串行配置存储器(Erasable Programmable Configurable Serial,EPCS)驱动和下载调试器等处理器的辅助单元.通过FPGA开发软件Quartus II中的Qsys工具快速构建硬件片上系统,利用灵活的Paralle I/O IP核配置双端口静态随机存取存储器(Static Random-Access Memory,SRAM)和信号采集模块的接口.

信号采集接口板主要用于完成对信号采集模块的参数配置以及回波数据的上传.接口板与信号采集模块之间通过PC104接口连接,板上有4个PC104接口,因此可以连接4个单通道、双通道、四通道甚至更多通道的信号采集模块.信号采集接口板与数据传输接口板之间通过光纤链路进行数据传输.其结构如图2所示.

图2

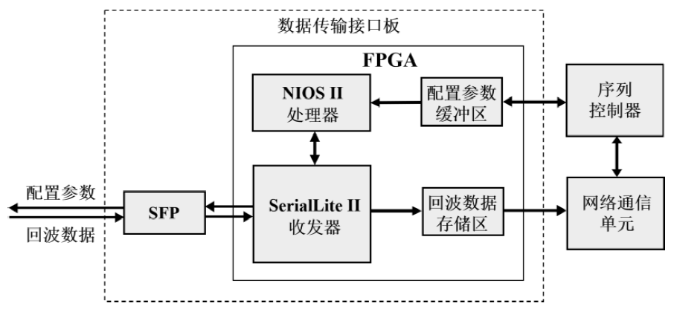

1.3 数据传输接口板

数据传输接口板的结构如图3所示.该电路采用的FPGA芯片和光模块与信号采集接口板的相同,FPGA中同样构建了SerialLite II收发器与NIOS II处理器.数据传输接口板连接序列控制器和网络通信单元.数据传输接口板用于完成两个工作:一是完成配置参数的发送,当NIOS II处理器接收到来自序列控制器的配置参数后,通过光纤链路将配置参数发送到信号采集接口板;二是接收回波数据,通过光纤链路接收到来自信号采集接口板的回波数据后,存入存储区中,当采集完毕一行数据后,通知网络通信单元并由其读出数据.

图3

1.4 电路硬件设计

信号采集接口板、数据传输接口板和信号采集模块的电路实物如图4所示.

图4

图4

(a)信号采集接口板电路图;(b)数据传输接口板电路图;(c)单通道信号采集模块电路图

Fig. 4

Circuit boards of (a) interface board for signal acquisition, (b) interface board for data transmission,and (c) single-channel signal acquisition module

信号采集接口板有4个SFP光纤口:两个采用PCML电平用于SerialLite II协议的数据传输,光纤的传输速率经测试为1.44 Gbps;另外两个采用低电压差分信号(Low-Voltage Differential Signaling,LVDS)电平可用于同步时钟的传输.具有四个信号采集模块的接口,每个接口包含控制总线、时钟、I/Q数据等,可以支持单路回波信号的采集.接口信号与FPGA相连,其定义具有较高的灵活性,如果将多个通道的采集集成于一个信号采集模块,并加上一定的控制逻辑,本设计将能够支持8个甚至16个接收通道.

数据传输接口板同样有4个SFP光纤口,与信号采集接口板的光纤口相对应.数据传输接口板通过与谱仪的接口连接序列控制器,接收数字信号处理器(Digital Signal Processor,DSP)发来的参数,并且连接网络通信单元以将采集到的回波数据上传到用户计算机.

信号采集模块实现对回波信号的采集,其功能包括可控增益放大、前置低通滤波、模数转换、数字正交解调(直接下变频).前置低通滤波器截止频率为17 MHz,模数转换器(Analog to Digital Converter,ADC)为AD公司的LTC2215,采样频率为60 MHz,因此射频频率范围覆盖为0~17 MHz,可以在0.4 T及以下场强的磁共振成像系统中工作.如果采用截止频率更高的低通滤波器,可以支持更高场强的低场磁共振成像系统(为实现1 T以上的高场信号采集,需配备变频电路).数字下变频器为AD公司的AD6620,解调出的I、Q信号字长为16 bit.

在信号采集接口板与信号采集模块的设计中,避免使用含铁磁材料的射频变压器与电感等器件,以便今后在屏蔽室强磁场环境下进行成像实验.

2 数据传输系统软件设计

软件设计包括SerialLite II协议的实现、基于NIOS II处理器的参数配置、磁共振成像的相干接收设计和回波数据上传4个部分.

2.1 SerialLite II协议实现

图5

链路支持检错重发,在发射机的链路层对将发送的数据循环冗余校核(Cyclic Redundancy Check,CRC)编码,在接收机的链路层对接收到的数据进行CRC验证,只有验证无误的数据会被传送到Atlantic接口,当接收到的数据包有误时,链路会重新传送该数据包.链路支持流控制,当接收机先进先出存储器(First Input First Output,FIFO)中的数据量超过设定的阈值时,会向发射机发出停止发送的信号,直到FIFO中填充的数据量低于该阈值.

2.1.1 链路的初始化与配置

链路可以通过硬件复位、软件复位和断链需要重连时初始化.通过发送和接收已知字符序列来完成字符对齐和通道对齐,当所有通道两端对应的发射机和接收机完成锁定后,链路建立完成.链路建立完成后,链路控制接口仍处于初始态,只有处于此态,接口才能响应向链路发出的数据传输请求.响应请求后Atlantic接口从存储区中取出包大小的数据,依次推入链路FIFO中.

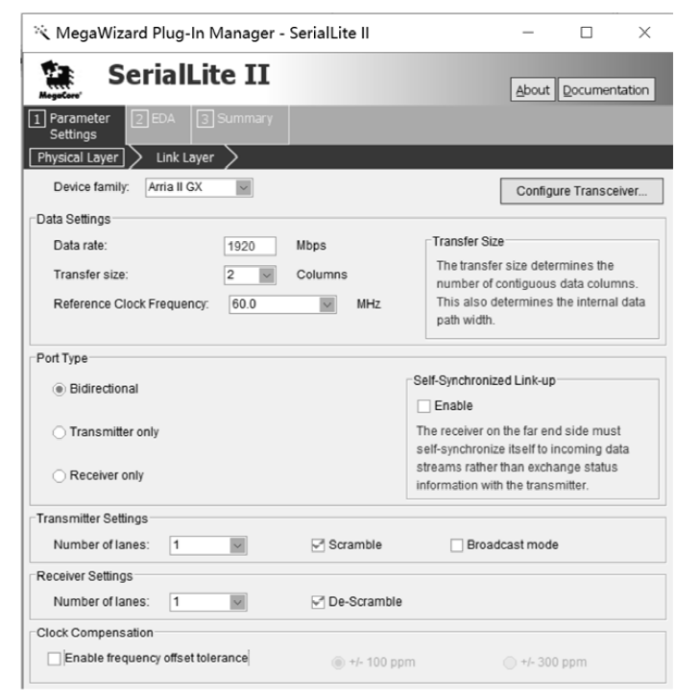

基于回波数据的特点,本设计中,链路选择全双工的包模式进行数据传输,单个数据包大小64×16 bit,链路通道的宽度设置为16 bit,链路FIFO大小1 024×16 bit.参考时钟60 MHz,为降低出错重传的次数,通道线速度选择为1.92 Gbps.Quartus II中SerialLite II的IP核实现与配置如图6所示.

图6

图6

SerialLite II IP核的实现与配置

Fig. 6

Implementation and configuration of SerialLite II IP core

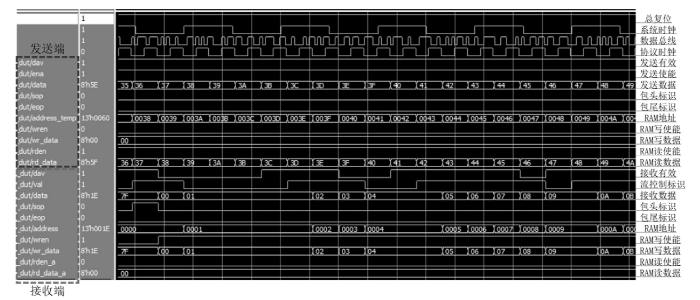

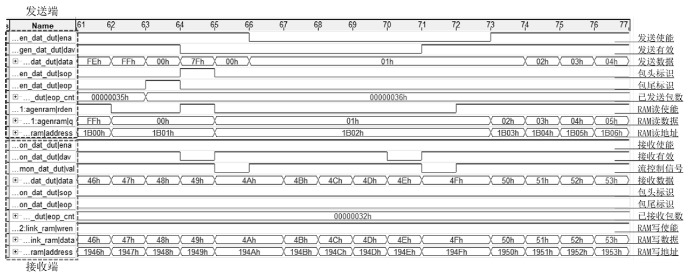

2.1.2 链路功能仿真

使用Modelsim软件对基于SerialLite II协议的数据传输做功能仿真,仿真的波形如图7所示.当包头标识符sop和dav信号(链路建立完成信号,高有效)为高电平时,开始从数据存储缓冲区中取出数据,然后推入链路FIFO并发出,直到包尾标识符eop为高电平时,当前数据包发送完成.在接收端当包头标识符sop,val信号(流控制信号,高有效)和dav信号为高电平时,开始往数据存储缓冲区中存入数据,直到包尾标识符eop为高电平时,当前数据包接收完成.

图7

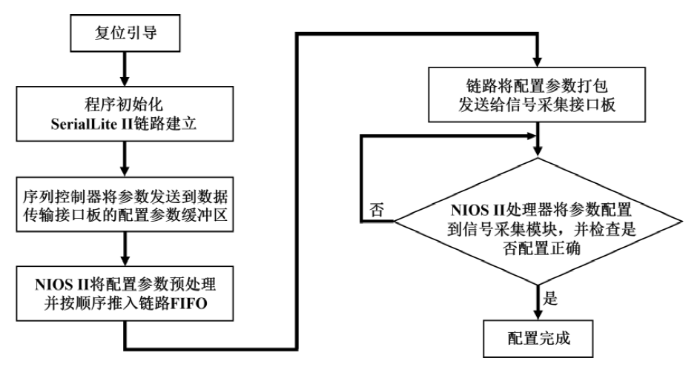

2.2 基于NIOS II处理器的参数配置

NIOS II软核处理器主要负责信号采集过程中参数(命令字)的接收与配置.数据传输接口板的NIOS II处理器接收序列控制器的DSP处理器发来的参数(如增益、频率、相位、滤波器系数、同步信号等),将其通过光纤传送到信号采集接口板.信号采集接口板的NIOS II处理器接收到参数后,将其写入到各信号采集模块的相关器件中.该配置过程如图8所示.

图8

图8

数据传输系统的参数配置流程

Fig. 8

Parameter configuration process of the data transmission system

由于信号接收需要配置的参数较多并且复杂,如果直接采用硬件描述语言编写FPGA程序存在可读性较差,不易维护与修改等缺点.NIOS II软核处理器的编程采用C语言,相比于硬件描述语言实现简单,代码的可读性更高且便于维护.

2.3 发射与接收相干性的时序设计

射频发射与接收的相干性是磁共振成像的一个基本要求[21].在本设计中,谱仪的射频发射单元与序列控制器插在一块背板上,序列控制器中的DSP处理器通过其外部并行总线进行直接的控制.信号采集模块与信号采集接口板在屏蔽室,序列控制器配置数据传输接口板,通过光纤对回波信号接收进行控制.因此,需要对控制的时序进行协同设计以保持射频发射与接收的相干性.

从两方面设计以保持相干性:一是发射与采集的时钟频率相同;二是发射与采集的控制在时间上对齐,即每次的回波采集中发射与接收的控制其延时固定.

谱仪采用一个60 MHz的恒温晶振作为设备的时钟,该时钟经过驱动后,一路送往射频发射单元,作为射频发射(采用直接数字合成技术)的工作时钟,另一路送往数据传输接口板的FPGA,再通过光纤传送到位于屏蔽室的信号采集接口板的FPGA,由FPGA输出到各信号采集模块,作为采集的时钟.这样,发射与采集的时钟来自同一时钟源,具有相同的频率.

基于SerialLite II协议的光纤数据传输在延时上并不完全固定,存在一定的抖动(范围有数十纳秒),因此需要进行时序的设计,以确保每次的回波采集中,发射与接收的控制其延时固定.为了实现这一点,在光纤数据传输的两端(即数据传输接口板的FPGA与信号采集接口板的FPGA)中各设置一个48 bit的计数器,计数器的时钟都是60 MHz.设备上电以后,将信号采集接口板的计数器的计数值设置为数据传输接口板的计数器的计数值减去一个差值,该差值乘以计数周期后比通过光纤传送一个数据包(8个16 bit)的延时最大值要稍大,这里取值为120.每一次DSP向数据传输接口板写入16 bit的信号采集的参数(命令字),在参数通过光纤下传的同时,也下传计数器的计数值.信号采集接口板的FPGA接收到参数与计数值后,进行延时等待,直到其自身的计数器的计数值等于下传的计数值,再将16 bit的参数或者命令发送到每一个信号采集模块.这样就能够保证在每次的回波采集中,发射与接收的控制其延时固定.

2.4 基于SerialLite II协议的回波数据上传

在磁共振扫描过程中,需要采集K空间中每一行的多通道回波数据,一行包括若干个点,每个点包含I、Q分量,每个分量16 bit,因此一次传输的数据量DN为M×N×4个字节,其中M为通道数量,N为一行的点数.在成像过程中,信号采集触发脉冲到来后,信号采集接口板的FPGA读取各接收通道输出的回波数据,存储到片内的数据存储区之中,完成一行数据的采集与打包后,通过SerialLite收发器将DN个字节的数据发送到数据传输接口板的FPGA,保存到数据存储区中,并向网络通信单元发出中断,网络通信单元中的通信处理器收到中断后,进入中断服务例程,从数据存储区中读出回波数据,并通过网络传送到用户计算机.

3 测试与实验

3.1 数据传输测试

分别用15 m和30 m长的光纤连接数据传输接口板和信号采集接口板,重复多次(这里为30次)数据传输实验.在数据传输的过程中,使用Quartus II的内嵌逻辑分析工具Signal-Tap2对链路信号进行抓取,结果如图9所示.

图9

从上图可以看出,当前发送端已发送包数为54(36 h),当包头标识信号sop和dav信号为高电平时,链路开始从RAM中取出第55个数据包要发送的数据(从00 h开始)并发送出去.在接收端,已接收包数为50(32 h),当前处于第51个数据包的接收过程中并不断将接收到的数据写入RAM中.以此可以判断信号抓取结果与图7功能仿真结果相符,这表明实现了SerialLite II协议的数据通信功能.

在Quartus II的In-System Memory Content Editor工具中分别查看两块接口板FPGA的配置参数缓冲区内容,图10给出了一个示例.

图10

图10

(a)数据传输接口板FPGA的配置数据缓冲区;(b)信号采集接口板FPGA的配置数据缓冲区

Fig. 10

(a) Configuration data buffer of the data transmission interface board FPGA; (b) Configuration data buffer of the signal acquisition interface board FPGA

实验表明,重复多次数据传输,结果均准确无误.实验中还测量了数据传输的平均延时,方法为:数据传输接口板FPGA发出一个参数,随即产生一个高有效脉冲,信号采集接口板FPGA收到该参数,随即也产生一个高有效脉冲,用示波器(泰克公司的DPO3034)测量这两个脉冲的时间间隔.测量得到的平均延时分别为380.3 ns(30 m光纤)与291.1 ns(15 m光纤).扣除信号在光纤线上传输带来的延时(30 m光纤约为150 ns,15 m光纤约为75 ns),实验结果与文献[22]结果(180 ns)基本相符,表明SerialLite II协议具有较低的传输延时.

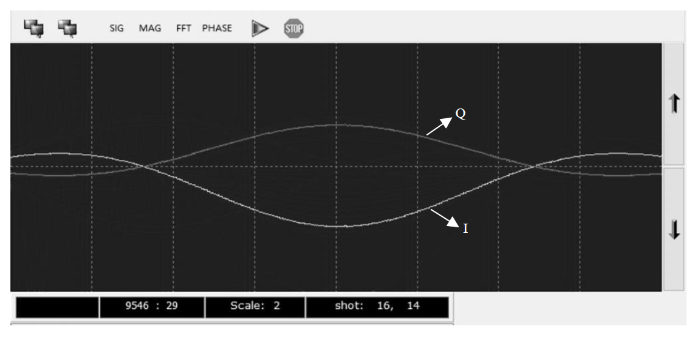

3.2 射频发射与接收的相干性测试

实验中采用专门设计的自发自收序列进行测试.即由信号采集模块采集射频发射模块输出的软脉冲,观测解调得到的I、Q波形.如果在多次循环中,每一次采集的I、Q波形保持不变,也即信号相位稳定,则可以判断发射与接收保持了相干性.

该自发自收序列的构成为:在重复的每一次回波采集中,首先发出指令对射频发射单元的直接数字合成器的数字本振进行同步,接着对信号采集模块的数字解调器的数字本振进行同步,之后延时一段时间,控制射频发射单元产生软脉冲,再控制信号采集模块对其进行采集.解调得到的I、Q数据通过信号采集接口板上传到数据传输接口板,最后传到用户计算机的扫描软件进行观测.实验所用的光纤线长度为30 m.

图11给出了实验结果的示例.软脉冲的频率为11.2 MHz,幅度约为峰峰800 mV,调制波形为拥有 1个主瓣与2个旁瓣的sinc波.接收带宽为100 kHz,采样点数为1 024.序列运行的重复次数为16,重复周期为300 ms.

图11

长时间的自发自收测试结果表明每一次的I、Q波形都不变,这说明采集的信号相位保持稳定,证实本设计实现和保持了发射与接收的相干性(自发自收测试视频见附件材料).

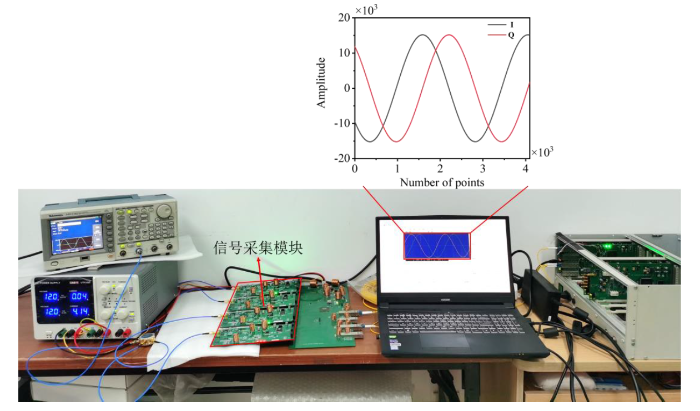

3.3 四通道信号采集实验

为了验证该数据传输系统的多通道信号采集与传输功能,我们制作了4个信号采集模块,将其与信号采集接口板连接,如图12所示.信号发生器(泰克公司的AFG3102)产生正弦波(频率为11.2 MHz,幅度为30 mV),先由功分器将信号一分为四,再将四路信号接入各信号采集模块进行采集.实验所用的光纤线长度为30 m.

图12

信号采集接口板把下传的配置参数配置到4个信号采集模块中,进行四通道的信号采集,接收带宽为500 kHz,调整增益使得I/Q数据的幅度接近动态范围.采集的数据上传到数据传输接口板,由谱仪的网络通信单元通过网络上传到用户计算机,在计算机上的扫描软件进行显示.

对不同的采样点数的数据传输进行重复测试(30次),测试结果表明,传输链路稳定,未丢失数据包,未发生数据错误.数据上传所需时间的测量方法为:信号采集接口板FPGA在发出第一个数据之前,产生一个高有效脉冲,数据传输接口板在收到并存储最后一个数据之后,产生一个高有效脉冲,用示波器测量这两个脉冲的时间间隔.测量结果如表1所示.

表1 四通道采集数据通过光纤上传所需的时间

Table 1

| 单个通道采集点数 | 平均所需时间/µs | 标准差/µs |

|---|---|---|

| 256 | 23.42 | 0.010854 |

| 512 | 45.82 | 0.010981 |

| 1024 | 91.16 | 0.010334 |

| 2048 | 182.4 | 0.011059 |

| 4096 | 364.2 | 0.010483 |

4 结论

本文基于SerialLite II协议与NIOS II处理器设计开发了基于光纤的数据传输系统,以用于磁共振成像信号采集.电路以FPGA与SFP模块为核心,FPGA中运行SerialLite II协议并构建NIOS II处理器,实现了信号采集配置参数的下传与回波数据的上传,保持了发射与接收的相干性.实验结果表明,所开发的数据传输系统能够高速、可靠地实现数据传输,从而为高性能成像谱仪的研制提供了技术支撑.

本设计尚未进行实际的磁共振成像实验,我们将在今后的工作中加快进行相关实验,以改善成像质量,实现其应用价值.

利益冲突

无

附件材料

自发自收测试视频

(可在《波谱学杂志》期刊官网

参考文献

A design of short dead-time RF coil and RF switch for low-field NMR

[J].

低场核磁共振短死时间射频线圈与射频开关的设计

[J].

The simulation design of a multi-channel receive-only coil for a given macaque

[J].

猕猴脑部定制多通道接收线圈的仿真设计

[J].

A high-field magnetic resonance imaging spectrometer using an oven-controlled crystal oscillator as the local oscillator of its radio frequency transceiver

[J].DOI:10.1063/1.4894657 URL [本文引用: 1]

Optical MR receive coil array interconnect

[C]//

A direct modulated optical link for MRI RF receive coil interconnection

[J].Optical glass fiber is a promising alternative to traditional coaxial cables for MRI RF receive coil interconnection to avoid any crosstalk and electromagnetic interference between multiple channels. A direct modulated optical link is proposed for MRI coil interconnection in this paper. The link performances of power gain, frequency response and dynamic range are measured. Phantom and in vivo human head images have been demonstrated by the connection of this direct modulated optical link to a head coil on a 0.3T MRI scanner for the first time. Comparable image qualities to coaxial cable link verify the feasibility of using the optical link for imaging with minor modification on the existing scanners. This optical link could also be easily extended for multi-channel array interconnections at high field of 1.5 T.

Magnetic resonance imaging with optical preamplification and detection

[J].

DOI:10.1038/s41598-019-54200-3

PMID:31796770

[本文引用: 1]

Magnetic resonance (MR) imaging relies on conventional electronics that is increasingly challenged by the push for stronger magnetic fields and higher channel count. These problems can be avoided by utilizing optical technologies. As a replacement for the standard low-noise preamplifier, we have implemented a new transduction principle that upconverts an MR signal to the optical domain and imaged a phantom in a clinical 3 T scanner with signal-to-noise comparable to classical induction detection.

Multi-channel MRI receiving module based on single-chip FPGA

[J].

基于单片FPGA的多通道磁共振成像接收模块

[J].

Effect of signal intensity inhomogeneity correction on quantitative susceptibility mapping of brain

[J].

均匀性校正在颅脑定量磁化率成像中的应用价值评估

[J].

Optimized 64-channel array configurations for accelerated simultaneous multislice acquisitions in 3T cardiac MRI

[J].

DOI:10.1002/mrm.28843

PMID:34028882

[本文引用: 1]

Three 64-channel cardiac coils with different detector array configurations were designed and constructed to evaluate acceleration capabilities in simultaneous multislice (SMS) imaging for 3T cardiac MRI.Three 64-channel coil array configurations obtained from a simulation-guided design approach were constructed and systematically evaluated regarding their encoding capabilities for accelerated SMS cardiac acquisitions at 3T. Array configuration A consists of uniformly distributed equally sized loops in an overlapped arrangement, B uses a gapped array design with symmetrically distributed equally sized loops, and C has non-uniform loop density and size, where smaller elements were centered over the heart and larger elements were placed surrounding the target region. To isolate the anatomic variation from differences in the coil configurations, all three array coils were built with identical semi-adjustable housing segments. The arrays' performance was compared using bench-level measurements and imaging performance tests, including signal-to-noise ratio (SNR) maps, array element noise correlation, and SMS acceleration capabilities. Additionally, all cardiac array coils were evaluated on a healthy volunteer.The array configuration C with the non-uniformly distributed loop density showed the best overall cardiac imaging performance in both SNR and SMS encoding power, when compared to the other constructed arrays. The diffusion weighted cardiac acquisitions on a healthy volunteer support the favorable accelerated SNR performance of this array configuration.Our results indicate that optimized highly parallel cardiac arrays, such as the 64-channel coil with a non-uniform loop size and density improve highly accelerated SMS cardiac MRI in comparison to symmetrically distributed loop array designs.© 2021 International Society for Magnetic Resonance in Medicine.

Design of multi-channel magnetic resonance signal acquisition based on FPGA

[J].

基于FPGA的多路磁共振信号采集设计

[J].

A home-built digital optical MRI console using high-speed serial links

[J].

DOI:10.1002/mrm.25403

PMID:25105249

[本文引用: 2]

To develop a high performance, cost-effective digital optical console for scalable multichannel MRI.The console system was implemented with flexibility and efficiency based on a modular architecture with distributed pulse sequencers. High-speed serial links were optimally utilized to interconnect the system, providing fast digital communication with a multi-gigabit data rate. The conventional analog radio frequency (RF) chain was replaced with a digital RF manipulation. The acquisition electronics were designed in close proximity to RF coils and preamplifiers, using a digital optical link to transmit the MR signal.A prototype of the console was constructed with a broad frequency range from direct current to 100 MHz. A temporal resolution of 1 μs was achieved for both the RF and gradient operations. The MR signal was digitized in the scanner room with an overall dynamic range between 16 and 24 bits and was transmitted to a master controller over a duplex optic fiber with a high data rate of 3.125 gigabits per second. High-quality phantom and human images were obtained using the prototype on both 0.36T and 1.5T clinical MRI scanners.A homemade digital optical MRI console with high-speed serial interconnection has been developed to better serve imaging research and clinical applications.© 2014 Wiley Periodicals, Inc.

A reconfigurable platform for magnetic resonance data acquisition and processing

[J].DOI:10.1109/TMI.42 URL [本文引用: 1]

An in-bore receiver for magnetic resonance imaging

[J].DOI:10.1109/TMI.42 URL [本文引用: 1]

Aurora 64B/66B LogiCORE IP Product Guide (v12.0)

[EB/OL].

Research on digital optical fiber transmission technique for magnetic resonance imaging

[J].

磁共振成像中数字光纤传输技术研究

[J].

SerialLite II Protocol Reference Manual

[EB/OL].

SerialLite II IP Core User Guide

[EB/OL].

Nios II Processor Reference Guide

[EB/OL].

Development of Altera NIOS II Soft-core system to predict total Hemoglobin using multivariate analysis

[J].

Phase coherence technology of digital MR console based on dual reference sources

[J].

基于双参考源的数字磁共振控制台相位相干技术

[J].